SDAccel™ 开发环境可将数据中心应用加速性能功耗比提高达 25 倍。

SDAccel 是 SDx™ 系列产品之一,提供一个编译器、一个调试器和一个分析器, 不仅支持标准 OpenCL API,可抽象硬件平台,而且还可优化针对硬件的代码,就像在 FPGA 加速电路板上运行的内核一样。

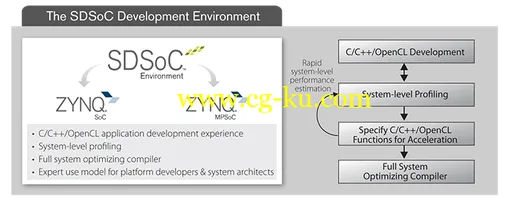

SDSoC™ 开发环境可为异构 Zynq®SoC 及 MPSoC 部署提供类似嵌入式 C/C++/OpenCL 应用的开发体验,其中包括简单易用的 Eclipse IDE 和综合设计环境。

SDSoC 提供业界首款 C/C++/OpenCL 全系统优化编译器,可实现系统级的特性描述、可编程逻辑中的自动软件加速、自动系统连接生成以及可加速编程的各种库。

此外,它还可帮助最终用户及第三方平台开发人员快速定义、集成和验证系统级解决方案,为其最终用户实现定制化编程环境。

Xilinx OpenCV 库现已推出,包含 50 多项硬件优化 OpenCV 功能,包括 Gausian、 Median、Bilateral、Harris corner、 Canny edge detection、HoG、ORB、SVM、LK Optical Flow 及更多简单易用的 Eclipse IDE 可用于开发支持嵌入式 C/C++/OpenCL 应用的完整 Zynq SoC 和 MPSoC只需一点按钮,就可对可编程逻辑 (PL) 中的功能进行加速支持作为目标 OS 的裸机、Linux 与 FreeRTOS系统级的特性描述快速性能估算与面积估算可在几分钟内完成,包括 PS、数据通信以及 PL高速缓存、存储器以及总线利用率的自动运行时仪表可实现最佳总体系统架构的便捷生成与探索全系统优化编译器可将 C/C++/OpenCL 应用编译成全功能 Zynq SoC 与 MPSoC 系统可在生成 ARM 软件与 FPGA 比特流的可编程逻辑中实现自动功能加速不仅可优化系统连接,而且还支持吞吐量、时延以及面积权衡的快速系统探索面向平台开发人员的专家级使用模型通过业经验证方法实现的目标定制电路板可将现有的 Vivado 项目及软件项目转换成 SDSoC面向 Zynq 开发板的开发板支持包 (BSP) 现已开始提供,包括 ZC702、ZC706 以及第三方开发板和系统级模块 (SoM)(包括 Zedboard、Microzed、Zybo、Avnet 嵌入式视觉套件、视频和成像套件以及 SDR 套件等)。

请单击“开发板与模块”查看全面的 BSP 列表。

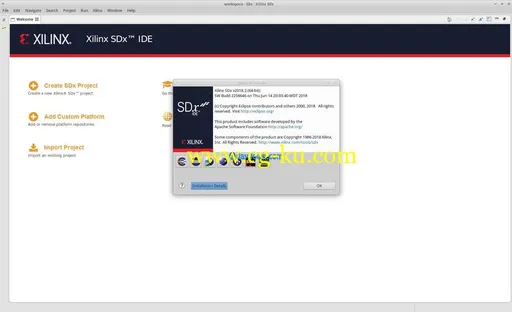

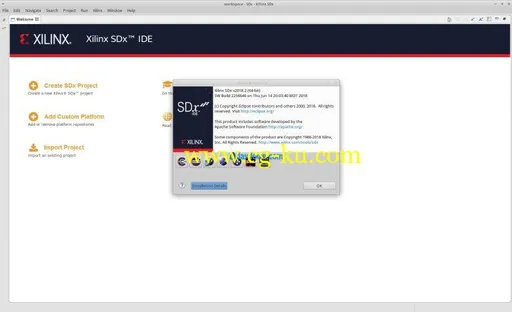

x64 | Language:English | File Size: 20.6 GBDescription:SDAccel is an OpenCL programming system, C / C ++ for heterogeneous systems with the implementation of hardware accelerators on Xilinx FPGA.

OpenCL is one of the applications of the C ++ language for the development of FPGA firmware.

SDAccel supports any combination of OpenCL, C, and C ++ cores with libraries for FPGA design.

This environment allows parallel programming of both the central processor and FPGA accelerators.

SDSoC development environment is intended only for Zynq (this is a chip in which there is a FPGA and an AWP processor in one package).

Add.

Information : Starting with version 2016.

3, SDAccel and SDSoC combined into one package called SDx.

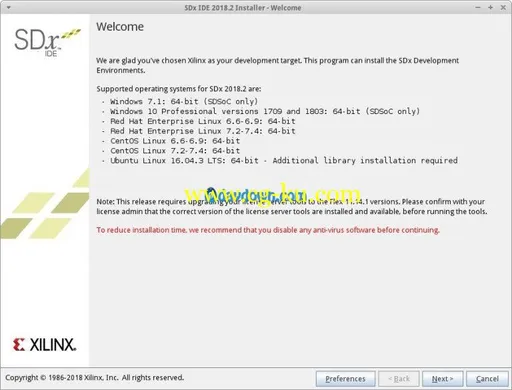

SDSoC works in Windows and Linux.

SDAccel only works under some versions of Linux.

SDSoC and SDAccel are characterized by the fact that the FPGA project already fades into the background.

In the foreground - the algorithm.

Both systems allow modeling at the level of the original algorithm written in C / C ++ and then translate it to FPGA.

This allows you to dramatically increase the complexity of the algorithm.

If we compare the programming for the FPGA on VHDL / Verilog and on C / C ++, then it begs the analogy between programming for conventional processors in C / C ++ and assembler.

In an assembler, you can make a more compact and fast code, and in C / C ++ you can write a more complex program.

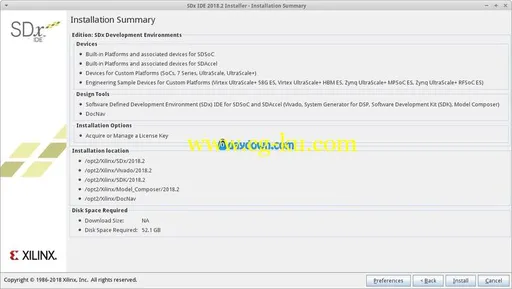

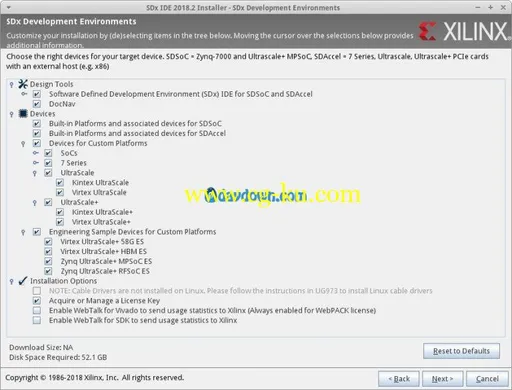

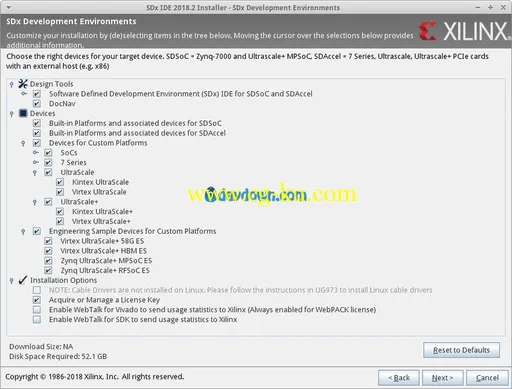

Details:Xilinx SDAccel/SDSoC 2018.2Year/Date of Release:2018Version:2018.2Developer:Xilinx Inc.

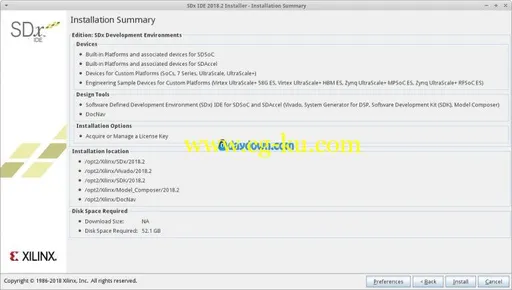

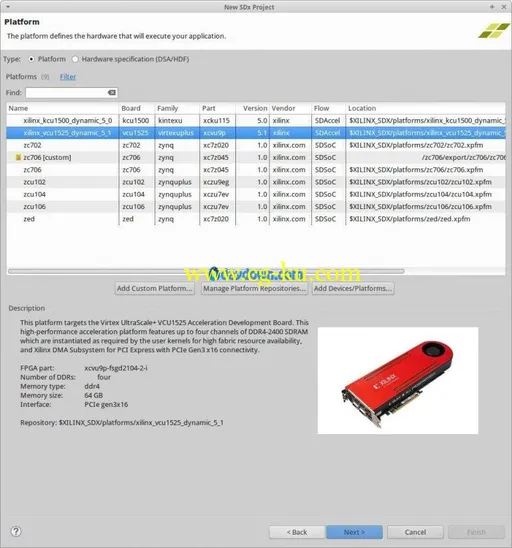

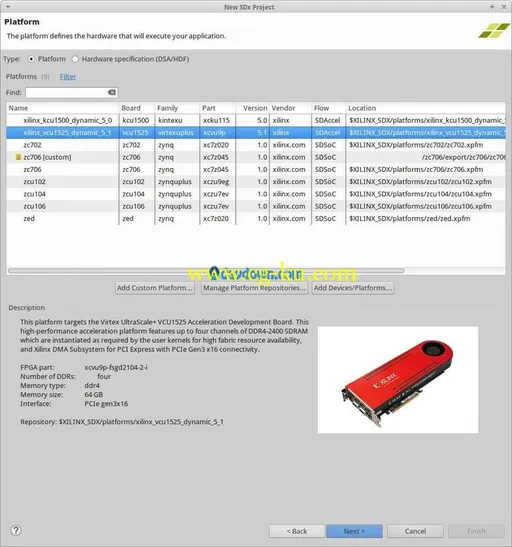

Architecture:64bitLanguage:EnglishMedicine:PresentSystem Requirements:System requirements SDAccel:The presence of one of the accelerators:-the Xilinx Kintex UltraScale KCU1500 the FPGA Reconfigurable Acceleration card based on XCKU115-FLVB2104-2 the FPGA-E,-the Xilinx the Virtex UltraScale + VCU1525 the FPGA Reconfigurable Acceleration card based on XCVU9P-L2FSGD2104E FPGA.

-Host computer for an accelerator with the characteristics Mat.

-card with support for PCIe Gen3 X8 slot,64GB OP,-Disk:100 GB of free hard disk space.

Computer for programming:PC with installed environment Vivado Design Suite 2018.

2 and Xilinx Platform Cable USB 2 (HW-USB-II-G).

OS Red Hat Enterprise Workstation / Server 7.3-7.4 (64-bit), CentOS 7.2, Ubuntu Linux 16.04.3 LTS (64-bit)SDSoC system requirements:One of the following developer platforms:-ZC702, ZC706, ZedBoard based on Zynq- 7000 SoC,-ZCU102, ZCU104, ZCU106 based on Zynq UltraScale + MPSoC.

For Windows version: Microsoft Windows 7 / 8.x / 10 Professional (64-bit)For Linux version: Red Hat Enterprise Workstation OS 6.7 / 6.8, Red Hat Enterprise Workstation Server / Server 7.3-7.4 (64-bit), CentOS 7.2 / 7.3 / 7.4 (64-bit), Ubuntu Linux 16.04.3 LTS (64-bit )

发布日期: 2018-10-23